2014-02-11

2014-02-10

Does the Raspberry Pi work with Windows? – Your tech questions answered - Colin Meaden

Does the Raspberry Pi work with Windows? – Your tech questions answered - Colin Meaden 2014feb09

http://www.theguardian.com/technology/2014/feb/09/your-tech-questions-answered-raspberry-pi

Do you have to use Linux with the Raspberry Pi or will Windows work with the system?

Q The Raspberry Pi is a brilliantly cheap way of getting young (and not so young) people into programming but, being Linux based, it is not to everyone's taste. Is there a low-cost equivalent – or DIY guide for sourcing components and building one – that will run Windows?

A The Raspberry Pi is an excellent little device, but it is compromised and likely to frustrate some users with its performance without some system tinkering. These limitations are arguably by design as it tries to encourage young people not to be afraid to explore what they can do with computers – this is where Linux is an excellent companion for the Pi. It makes it much easier to tinker with the core of the system or, if you get more proficient, even compile your own version of the operating system. (Compiling is when you pass in computer code, and a compiler breaks it down into the most basic instructions so that a computer processor can act on them.) Linux may not be quite as user-friendly, but it's incredibly flexible for learning and has amazing package managers to install compilers easily, as well as to install other software. This also has the benefit that, if you ruin the system, you can re-image (clear off and re-add a new version of the OS) the SD card and start again.

If you require a Windows computer, however (for example, if its primary use is going to be office tasks with some light programming), it's hard to recommend anything close to that price point. This is because Windows is a much more bloated operating system and requires higher system specifications to operate and run well. You also have to be careful that you aren't buying a Windows RT device, as you won't be able to run your own code without some more setup and, even then, you'll be limited to which languages you can write.

If you can afford the extra, and need Windows, then purchase as you would a home computer – but you'll have to be more careful with what you touch, especially if it has important files without backups.

...

Daniel is a freelance programmer for iOS and the web. He is a student and has been coding since he was eight. He is an ambassador for Young Rewired State ...

http://www.theguardian.com/technology/2014/feb/09/your-tech-questions-answered-raspberry-pi

Do you have to use Linux with the Raspberry Pi or will Windows work with the system?

Q The Raspberry Pi is a brilliantly cheap way of getting young (and not so young) people into programming but, being Linux based, it is not to everyone's taste. Is there a low-cost equivalent – or DIY guide for sourcing components and building one – that will run Windows?

A The Raspberry Pi is an excellent little device, but it is compromised and likely to frustrate some users with its performance without some system tinkering. These limitations are arguably by design as it tries to encourage young people not to be afraid to explore what they can do with computers – this is where Linux is an excellent companion for the Pi. It makes it much easier to tinker with the core of the system or, if you get more proficient, even compile your own version of the operating system. (Compiling is when you pass in computer code, and a compiler breaks it down into the most basic instructions so that a computer processor can act on them.) Linux may not be quite as user-friendly, but it's incredibly flexible for learning and has amazing package managers to install compilers easily, as well as to install other software. This also has the benefit that, if you ruin the system, you can re-image (clear off and re-add a new version of the OS) the SD card and start again.

If you require a Windows computer, however (for example, if its primary use is going to be office tasks with some light programming), it's hard to recommend anything close to that price point. This is because Windows is a much more bloated operating system and requires higher system specifications to operate and run well. You also have to be careful that you aren't buying a Windows RT device, as you won't be able to run your own code without some more setup and, even then, you'll be limited to which languages you can write.

If you can afford the extra, and need Windows, then purchase as you would a home computer – but you'll have to be more careful with what you touch, especially if it has important files without backups.

...

Daniel is a freelance programmer for iOS and the web. He is a student and has been coding since he was eight. He is an ambassador for Young Rewired State ...

.END

2014-02-09

2014-02-08

The Connected Home: Which Board is Right for Me? By Alasdair Allan

The Connected Home: Which Board is Right for Me? By Alasdair Allan Posted 02/07/2014

http://makezine.com/magazine/make-36-boards/which-board-is-right-for-me/

...

So, um, which board should I buy anyway?

.END

http://makezine.com/magazine/make-36-boards/which-board-is-right-for-me/

...

So, um, which board should I buy anyway?

Because of the communities that have grown up around them, I would unhesitatingly recommend an Arduino if you need an 8-bit microcontroller, or a Raspberry Pi if you need a single-board computer running Linux.

If you’re leaning toward the Pi, but worried it may not suit your application, the decision gets more complex. The Raspberry Pi is yet to become an unstoppable force, or an immovable object, like the Arduino. The most serious alternative, around the same price point, is BeagleBone Black. On the other hand, BeagleBone Black is relatively new, and its community is much smaller, so you might end up having to solve a lot of your own problems.

If you’re leaning toward an Arduino, but have specific needs (like wireless connectivity) that it doesn’t meet out of the box, then you should probably look first among the myriad of Arduino derivatives. You’ll probably find your desired feature set baked right into one of them.

Finally, if your project’s I/O requirements permit it, take a serious look at the TI LaunchPad MSP430. Its low-price, low-power requirements, and user-friendly development environment make a very strong case.

.END

2014-02-06

2014-02-04

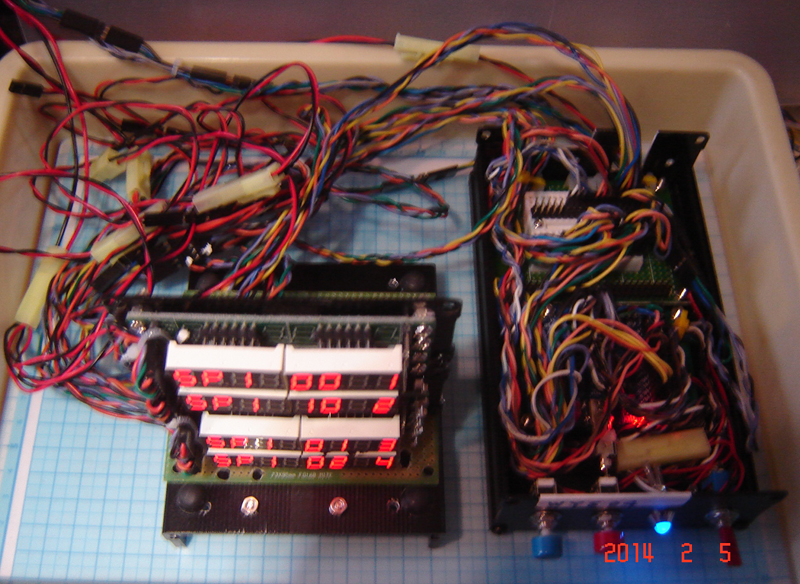

I2C testing notes - scope standby to display SCL, SDA signals

I2C testing notes - RMB2,000 Atten ADS1102CAL 2 channel wide screen digital storage scope standby to display SCL, SDA signals

.END

2014-02-03

Coocox I2C EEPROM example code reading notes 1

// ***************************************************************************

I2C_M_SETUP_Type transferMCfg; // I2C xmit/recv control/data structure

// ***************************************************************************

// I2C_M_SETUP_Type;

typedef struct

{

uint32_t sl_addr7bit; /**< Slave address in 7bit mode */

uint8_t* tx_data; /**< Pointer to Transmit data - NULL if data transmit

is not used */

uint32_t tx_length; /**< Transmit data length - 0 if data transmit

is not used*/

uint32_t tx_count; /**< Current Transmit data counter */

uint8_t* rx_data; /**< Pointer to Receive data - NULL if data receive

is not used */

uint32_t rx_length; /**< Receive data length - 0 if data receive is

not used */

uint32_t rx_count; /**< Current Receive data counter */

uint32_t retransmissions_max; /**< Max Re-Transmission value */

uint32_t retransmissions_count; /**< Current Re-Transmission counter */

uint32_t status; /**< Current status of I2C activity */

void (*callback)(void); /**< Pointer to Call back function when transmission complete

used in interrupt transfer mode */

} I2C_M_SETUP_Type;

// ***************************************************************************

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, ENABLE); // Enable then disable

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, DISABLE); // why this order?

// ***************************************************************************

/*********************************************************************//**

* @brief Reset the SPI or I2C peripherals

* @param[in] Periph it can be

* - SYSCON_RSTPeriph_SSP0 : Reset SSP0

* - SYSCON_RSTPeriph_I2C : Reset I2C

* - SYSCON_RSTPeriph_SSP1 : Reset SSP1

* NewState new state of the specified peripheral, it can be:

* - ENABLE : Resets the peripheral

* - DISABLE : Peripheral reset de-asserted

* @return none

**********************************************************************/

void SYSCON_PeriphResetCmd(uint32_t Periph, FunctionalState NewState)

{

if(NewState == ENABLE) {

LPC_SYSCON->PRESETCTRL &= (~Periph) & 0x7;

} else if (NewState == DISABLE) {

LPC_SYSCON->PRESETCTRL |= Periph & 0x7;

}

}

// ***************************************************************************

I2C_PinsInit(I2CMODE_SF); // Set SCL/SDA(P04/P05) mode = Standard Fast

I2C_Init(LPC_I2C, 100000); // Set I2C peripheral clock rate = 100kHz

I2C_Cmd(LPC_I2C, ENABLE); // Enable I2C operation

// ***************************************************************************

/********************************************************************//**

* @brief Init I2C SDA and SCL pins, pins assign:

* I2C SCL : PIO0_4

* I2C SDA : PIO0_5

* @param[in] mod, i2c mode, it can be

* -I2CMODE_SF : Standard mode/ Fast-mode I2C

* -I2CMODE_SIO : Standard I/O functionality

* -I2CMODE_FP : Fast-mode Plus I2C

* @return None

*********************************************************************/

void I2C_PinsInit(I2CMODE_Typedef mod)

{

IOCON_SetPinFunc(IOCON_PIO0_4, PIO0_4_FUN_SCL); /* I2C SCL - PIO0_4 */

IOCON_SetPinFunc(IOCON_PIO0_5, PIO0_5_FUN_SDA); /* I2C SDA - PIO0_5 */

IOCON_SetI2CMode(IOCON_PIO0_4, mod);

IOCON_SetI2CMode(IOCON_PIO0_5, mod);

}

/********************************************************************//**

* @brief Initializes the I2Cx peripheral with specified parameter.

*

* @param[in] I2Cx I2C peripheral selected, should be LPC_I2C

* @param[in] clockrate Target clock rate value to initialized I2C

* peripheral

* @return None

*********************************************************************/

void I2C_Init(I2C_TypeDef *I2Cx, uint32_t clockrate)

{

CHECK_PARAM(PARAM_I2Cx(I2Cx));

/* Enable I2C clock */

SYSCON_AHBPeriphClockCmd (SYSCON_AHBPeriph_I2C, ENABLE);

/* Set clock rate */

I2C_SetClock(I2Cx, clockrate);

/* Set I2C operation to default */

I2Cx->CONCLR = (I2C_I2CONCLR_AAC | I2C_I2CONCLR_STAC | I2C_I2CONCLR_I2ENC);

}

/*********************************************************************//**

* @brief Enable or disable I2C peripheral's operation

* @param[in] I2Cx I2C peripheral selected, LPC_I2C

* @param[in] NewState New State of I2Cx peripheral's operation

* @return none

**********************************************************************/

void I2C_Cmd(I2C_TypeDef* I2Cx, FunctionalState NewState)

{

CHECK_PARAM(PARAM_FUNCTIONALSTATE(NewState));

CHECK_PARAM(PARAM_I2Cx(I2Cx));

if (NewState == ENABLE)

{

I2Cx->CONSET = I2C_I2CONSET_I2EN;

}

else

{

I2Cx->CONCLR = I2C_I2CONCLR_I2ENC;

}

}

// ***************************************************************************

unsigned char send_buf[10] = {0,0, 1,2,3,4,5,6,7};

unsigned char rece_buf[10] = {0};

// ***************************************************************************

// ***************************************************************************

transferMCfg.sl_addr7bit = 0xA0>>1; // Standard EEPROM 7 bit address = 1010000

transferMCfg.tx_data = send_buf; // Send data in send buffer

transferMCfg.tx_length = 8; // Send 8 bits

transferMCfg.rx_data = NULL; // Receive buffer not used

transferMCfg.rx_length = 0; // Receive buffer length = 0

transferMCfg.retransmissions_max = 3; // maximum try 3 times

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

// send polling mode

// ***************************************************************************

// ***************************************************************************

for(i=0;i<100;i++) // Delay for EEPROM operation

{

for(j=0;j<1000;j++);

}

// ***************************************************************************

// ***************************************************************************

transferMCfg.tx_data = send_buf; // Send

transferMCfg.tx_length = 2; // 2 zero bits to EEPROM

transferMCfg.rx_data = rece_buf; // Receive

transferMCfg.rx_length = 6; // 6 data bits from EEPROM

transferMCfg.retransmissions_max = 3; // Maximum try 3 times

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

// receive in polling mode

// ***************************************************************************

I2C_M_SETUP_Type transferMCfg; // I2C xmit/recv control/data structure

// ***************************************************************************

// I2C_M_SETUP_Type;

typedef struct

{

uint32_t sl_addr7bit; /**< Slave address in 7bit mode */

uint8_t* tx_data; /**< Pointer to Transmit data - NULL if data transmit

is not used */

uint32_t tx_length; /**< Transmit data length - 0 if data transmit

is not used*/

uint32_t tx_count; /**< Current Transmit data counter */

uint8_t* rx_data; /**< Pointer to Receive data - NULL if data receive

is not used */

uint32_t rx_length; /**< Receive data length - 0 if data receive is

not used */

uint32_t rx_count; /**< Current Receive data counter */

uint32_t retransmissions_max; /**< Max Re-Transmission value */

uint32_t retransmissions_count; /**< Current Re-Transmission counter */

uint32_t status; /**< Current status of I2C activity */

void (*callback)(void); /**< Pointer to Call back function when transmission complete

used in interrupt transfer mode */

} I2C_M_SETUP_Type;

// ***************************************************************************

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, ENABLE); // Enable then disable

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, DISABLE); // why this order?

// ***************************************************************************

/*********************************************************************//**

* @brief Reset the SPI or I2C peripherals

* @param[in] Periph it can be

* - SYSCON_RSTPeriph_SSP0 : Reset SSP0

* - SYSCON_RSTPeriph_I2C : Reset I2C

* - SYSCON_RSTPeriph_SSP1 : Reset SSP1

* NewState new state of the specified peripheral, it can be:

* - ENABLE : Resets the peripheral

* - DISABLE : Peripheral reset de-asserted

* @return none

**********************************************************************/

void SYSCON_PeriphResetCmd(uint32_t Periph, FunctionalState NewState)

{

if(NewState == ENABLE) {

LPC_SYSCON->PRESETCTRL &= (~Periph) & 0x7;

} else if (NewState == DISABLE) {

LPC_SYSCON->PRESETCTRL |= Periph & 0x7;

}

}

// ***************************************************************************

I2C_PinsInit(I2CMODE_SF); // Set SCL/SDA(P04/P05) mode = Standard Fast

I2C_Init(LPC_I2C, 100000); // Set I2C peripheral clock rate = 100kHz

I2C_Cmd(LPC_I2C, ENABLE); // Enable I2C operation

// ***************************************************************************

/********************************************************************//**

* @brief Init I2C SDA and SCL pins, pins assign:

* I2C SCL : PIO0_4

* I2C SDA : PIO0_5

* @param[in] mod, i2c mode, it can be

* -I2CMODE_SF : Standard mode/ Fast-mode I2C

* -I2CMODE_SIO : Standard I/O functionality

* -I2CMODE_FP : Fast-mode Plus I2C

* @return None

*********************************************************************/

void I2C_PinsInit(I2CMODE_Typedef mod)

{

IOCON_SetPinFunc(IOCON_PIO0_4, PIO0_4_FUN_SCL); /* I2C SCL - PIO0_4 */

IOCON_SetPinFunc(IOCON_PIO0_5, PIO0_5_FUN_SDA); /* I2C SDA - PIO0_5 */

IOCON_SetI2CMode(IOCON_PIO0_4, mod);

IOCON_SetI2CMode(IOCON_PIO0_5, mod);

}

/********************************************************************//**

* @brief Initializes the I2Cx peripheral with specified parameter.

*

* @param[in] I2Cx I2C peripheral selected, should be LPC_I2C

* @param[in] clockrate Target clock rate value to initialized I2C

* peripheral

* @return None

*********************************************************************/

void I2C_Init(I2C_TypeDef *I2Cx, uint32_t clockrate)

{

CHECK_PARAM(PARAM_I2Cx(I2Cx));

/* Enable I2C clock */

SYSCON_AHBPeriphClockCmd (SYSCON_AHBPeriph_I2C, ENABLE);

/* Set clock rate */

I2C_SetClock(I2Cx, clockrate);

/* Set I2C operation to default */

I2Cx->CONCLR = (I2C_I2CONCLR_AAC | I2C_I2CONCLR_STAC | I2C_I2CONCLR_I2ENC);

}

/*********************************************************************//**

* @brief Enable or disable I2C peripheral's operation

* @param[in] I2Cx I2C peripheral selected, LPC_I2C

* @param[in] NewState New State of I2Cx peripheral's operation

* @return none

**********************************************************************/

void I2C_Cmd(I2C_TypeDef* I2Cx, FunctionalState NewState)

{

CHECK_PARAM(PARAM_FUNCTIONALSTATE(NewState));

CHECK_PARAM(PARAM_I2Cx(I2Cx));

if (NewState == ENABLE)

{

I2Cx->CONSET = I2C_I2CONSET_I2EN;

}

else

{

I2Cx->CONCLR = I2C_I2CONCLR_I2ENC;

}

}

// ***************************************************************************

unsigned char send_buf[10] = {0,0, 1,2,3,4,5,6,7};

unsigned char rece_buf[10] = {0};

// ***************************************************************************

// ***************************************************************************

transferMCfg.sl_addr7bit = 0xA0>>1; // Standard EEPROM 7 bit address = 1010000

transferMCfg.tx_data = send_buf; // Send data in send buffer

transferMCfg.tx_length = 8; // Send 8 bits

transferMCfg.rx_data = NULL; // Receive buffer not used

transferMCfg.rx_length = 0; // Receive buffer length = 0

transferMCfg.retransmissions_max = 3; // maximum try 3 times

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

// send polling mode

// ***************************************************************************

// ***************************************************************************

for(i=0;i<100;i++) // Delay for EEPROM operation

{

for(j=0;j<1000;j++);

}

// ***************************************************************************

// ***************************************************************************

transferMCfg.tx_data = send_buf; // Send

transferMCfg.tx_length = 2; // 2 zero bits to EEPROM

transferMCfg.rx_data = rece_buf; // Receive

transferMCfg.rx_length = 6; // 6 data bits from EEPROM

transferMCfg.retransmissions_max = 3; // Maximum try 3 times

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

// receive in polling mode

// ***************************************************************************

I2C Wikipedia reading notes

I2C - Wikipedia

I2C (Inter-Integrated Circuit, referred to as I-squared-C, I-two-C, or IIC) is a multimaster serial single-ended computer bus invented by the Philips semiconductor division, today NXP Semiconductors, and used for attaching low-speed peripherals to a motherboard, embedded system, cellphone, or other digital electronic devices.

...

SMBus, defined by Intel in 1995, is a subset of I2C that defines the protocols more strictly. One purpose of SMBus is to promote robustness and interoperability. Accordingly, modern I2C systems incorporate policies and rules from SMBus, sometimes supporting both I2C and SMBus, requiring only minimal reconfiguration.

...

I2C uses only two bidirectional open-drain lines, Serial Data Line (SDA) and Serial Clock (SCL), pulled up with resistors. Typical voltages used are +5 V or +3.3 V although systems with other voltages are permitted.

The I2C reference design has a 7-bit or a 10-bit (depending on the device used) address space. Common I2C bus speeds are the 100 kbit/s standard mode and the 10 kbit/s low-speed mode, but arbitrarily low clock frequencies are also allowed.

Recent revisions of I2C can host more nodes and run at faster speeds (400 kbit/s Fast mode, 1 Mbit/s Fast mode plus or Fm+, and 3.4 Mbit/s High Speed mode). These speeds are more widely used on embedded systems than on PCs. There are also other features, such as 16-bit addressing.

Note the bit rates are quoted for the transactions between master and slave without clock stretching or other hardware overhead. Protocol overheads include a slave address and perhaps a register address within the slave device as well as per-byte ACK/NACK bits. Thus the actual transfer rate of user data is lower than those peak bit rates alone would imply. For example, if each interaction with a slave inefficiently allows only 1 byte of data to be transferred, the data rate will be less than half the peak bit rate.

The maximum number of nodes is limited by the address space, and also by the total bus capacitance of 400 pF, which restricts practical communication distances to a few meters.

Reference design

The before mentioned reference design is a bus with a clock (SCL) and data (SDA) lines with 7-bit addressing. The bus has two roles for nodes: master and slave:

Master node — node that generates the clock and initiates communication with slaves

Slave node — node that receives the clock and responds when addressed by the master

The bus is a multi-master bus which means any number of master nodes can be present. Additionally, master and slave roles may be changed between messages (after a STOP is sent).

There are four potential modes of operation for a given bus device, although most devices only use a single role and its two modes:

master transmit — master node is sending data to a slave

master receive — master node is receiving data from a slave

slave transmit — slave node is sending data to the master

slave receive — slave node is receiving data from the master

The master is initially in master transmit mode by sending a start bit followed by the 7-bit address of the slave it wishes to communicate with, which is finally followed by a single bit representing whether it wishes to write(0) to or read(1) from the slave.

If the slave exists on the bus then it will respond with an ACK bit (active low for acknowledged) for that address. The master then continues in either transmit or receive mode (according to the read/write bit it sent), and the slave continues in its complementary mode (receive or transmit, respectively).

The address and the data bytes are sent most significant bit first. The start bit is indicated by a high-to-low transition of SDA with SCL high; the stop bit is indicated by a low-to-high transition of SDA with SCL high. All other transitions of SDA take place with SCL low.

If the master wishes to write to the slave then it repeatedly sends a byte with the slave sending an ACK bit. (In this situation, the master is in master transmit mode and the slave is in slave receive mode.)

If the master wishes to read from the slave then it repeatedly receives a byte from the slave, the master sending an ACK bit after every byte but the last one. (In this situation, the master is in master receive mode and the slave is in slave transmit mode.)

The master then either ends transmission with a stop bit, or it may send another START bit if it wishes to retain control of the bus for another transfer (a "combined message").

Message protocols

I2C defines basic types of messages, each of which begins with a START and ends with a STOP:

Single message where a master writes data to a slave;

Single message where a master reads data from a slave;

Combined messages, where a master issues at least two reads and/or writes to one or more slaves.

In a combined message, each read or write begins with a START and the slave address. After the first START in a combined message these are also called repeated START bits. Repeated START bits are not preceded by STOP bits, which is how slaves know the next transfer is part of the same message.

Any given slave will only respond to particular messages, as defined by its product documentation.

Pure I2C systems support arbitrary message structures. SMBus is restricted to nine of those structures ...

In practice, most slaves adopt request/response control models, where one or more bytes following a write command are treated as a command or address. Those bytes determine how subsequent written bytes are treated and/or how the slave responds on subsequent reads. Most SMBus operations involve single byte commands.

Messaging example: 24c32 EEPROM

One specific example is the 24c32 type EEPROM, which uses two request bytes that are called Address High and Address Low. (Accordingly, these EEPROMs are not usable by pure SMBus hosts, which only support single byte commands or addresses.)

These bytes are used to address bytes within the 32 kbit (4 kB) supported by that EEPROM; the same two byte addressing is also used by larger EEPROMs, such as 24c512 ones storing 512 kbits (64 kB).

Writing and reading data to these EEPROMs uses a simple protocol: the address is written, and then data is transferred until the end of the message. (That data transfer part of the protocol also makes trouble for SMBus, since the data bytes are not preceded by a count and more than 32 bytes can be transferred at once. I2C EEPROMs smaller than 32 kbits, such as 2 kbit 24c02 ones, are often used on SMBus with inefficient single byte data transfers.)

To write to the EEPROM, a single message is used. After the START, the master sends the chip's bus address with the direction bit clear (write), then sends the two byte address of data within the EEPROM and then sends data bytes to be written starting at that address, followed by a STOP. When writing multiple bytes, all the bytes must be in the same 32 byte page. While it is busy saving those bytes to memory, the EEPROM will not respond to further I2C requests. (That is another incompatibility with SMBus: SMBus devices must always respond to their bus addresses.)

To read starting at a particular address in the EEPROM, a combined message is used. After a START, the master first writes that chip's bus address with the direction bit clear (write) and then the two bytes of EEPROM data address. It then sends a (repeated) START and the EEPROM's bus address with the direction bit set (read). The EEPROM will then respond with the data bytes beginning at the specified EEPROM data address -— a combined message, first a write then a read. The master issues an ACK after each read byte except the last byte, and then a issues a STOP. The EEPROM increments the address after each data byte transferred; multi-byte reads can retrieve the entire contents of the EEPROM using one combined message.

Physical layer

At the physical layer, both SCL and SDA lines are of open-drain design, thus, pull-up resistors are needed. Pulling the line to ground is considered a logical zero while letting the line float is a logical one. This is used as a channel access method. High speed systems (and some others) also add a current source pull up, at least on SCL; this accommodates higher bus capacitance and enables faster rise times.

An important consequence of this is that multiple nodes may be driving the lines simultaneously. If any node is driving the line low, it will be low. Nodes that are trying to transmit a logical one (i.e. letting the line float high) can see this, and thereby know that another node is active at the same time.

When used on SCL, this is called clock stretching and gives slaves a flow control mechanism. When used on SDA, this is called arbitration and ensures there is only one transmitter at a time.

...

Clock stretching using SCL

...

Arbitration using SDA

...

Circuit interconnections

I2C is popular for interfacing peripheral circuits to prototyping systems, such as the Arduino and Raspberry Pi.

I2C does not employ a standardized connector, however, and board designers have created various wiring schemes for I2C interconnections. To minimize damage on 0.1-inch headers, some developers suggested to use alternating signal and power connections of the following wiring schemes should be used: (GND, SCL, VCC, SDA) or (VCC, SDA, GND, SCL).[4]

Buffering and multiplexing

When there are many I2C devices in a system, there can be a need to include bus buffers or multiplexers to split large bus segments into smaller ones. This can be necessary to keep the capacitance of a bus segment below the allowable value or to allow multiple devices with the same address to be separated by a multiplexer.

Many types of multiplexers and buffers exist and all must take into account the fact that I2C lines are specified to be bidirectional. Multiplexers can be implemented with analog switches which can tie one segment to another. Analog switches maintain the bidirectional nature of the lines but do not isolate the capacitance of one segment from another or provide buffering capability.

Buffers can be used to isolate capacitance on one segment from another and/or allow I2C to be sent over longer cables or traces. ...

Timing diagram

Data transfer sequence

Data transfer is initiated with the START bit (S) when SDA is pulled low while SCL stays high. Then, SDA sets the transferred bit while SCL is low (blue) and the data is sampled (received) when SCL rises (green). When the transfer is complete, a STOP bit (P) is sent by releasing the data line to allow it to be pulled up while SCL is constantly high. In order to avoid false marker detection, the level on SDA is changed on the falling edge and is captured on the rising edge of SCL.

Example of bit-banging the I2C Master protocol

...

.END

I2C (Inter-Integrated Circuit, referred to as I-squared-C, I-two-C, or IIC) is a multimaster serial single-ended computer bus invented by the Philips semiconductor division, today NXP Semiconductors, and used for attaching low-speed peripherals to a motherboard, embedded system, cellphone, or other digital electronic devices.

...

SMBus, defined by Intel in 1995, is a subset of I2C that defines the protocols more strictly. One purpose of SMBus is to promote robustness and interoperability. Accordingly, modern I2C systems incorporate policies and rules from SMBus, sometimes supporting both I2C and SMBus, requiring only minimal reconfiguration.

...

I2C uses only two bidirectional open-drain lines, Serial Data Line (SDA) and Serial Clock (SCL), pulled up with resistors. Typical voltages used are +5 V or +3.3 V although systems with other voltages are permitted.

The I2C reference design has a 7-bit or a 10-bit (depending on the device used) address space. Common I2C bus speeds are the 100 kbit/s standard mode and the 10 kbit/s low-speed mode, but arbitrarily low clock frequencies are also allowed.

Recent revisions of I2C can host more nodes and run at faster speeds (400 kbit/s Fast mode, 1 Mbit/s Fast mode plus or Fm+, and 3.4 Mbit/s High Speed mode). These speeds are more widely used on embedded systems than on PCs. There are also other features, such as 16-bit addressing.

Note the bit rates are quoted for the transactions between master and slave without clock stretching or other hardware overhead. Protocol overheads include a slave address and perhaps a register address within the slave device as well as per-byte ACK/NACK bits. Thus the actual transfer rate of user data is lower than those peak bit rates alone would imply. For example, if each interaction with a slave inefficiently allows only 1 byte of data to be transferred, the data rate will be less than half the peak bit rate.

The maximum number of nodes is limited by the address space, and also by the total bus capacitance of 400 pF, which restricts practical communication distances to a few meters.

Reference design

The before mentioned reference design is a bus with a clock (SCL) and data (SDA) lines with 7-bit addressing. The bus has two roles for nodes: master and slave:

Master node — node that generates the clock and initiates communication with slaves

Slave node — node that receives the clock and responds when addressed by the master

The bus is a multi-master bus which means any number of master nodes can be present. Additionally, master and slave roles may be changed between messages (after a STOP is sent).

There are four potential modes of operation for a given bus device, although most devices only use a single role and its two modes:

master transmit — master node is sending data to a slave

master receive — master node is receiving data from a slave

slave transmit — slave node is sending data to the master

slave receive — slave node is receiving data from the master

The master is initially in master transmit mode by sending a start bit followed by the 7-bit address of the slave it wishes to communicate with, which is finally followed by a single bit representing whether it wishes to write(0) to or read(1) from the slave.

If the slave exists on the bus then it will respond with an ACK bit (active low for acknowledged) for that address. The master then continues in either transmit or receive mode (according to the read/write bit it sent), and the slave continues in its complementary mode (receive or transmit, respectively).

The address and the data bytes are sent most significant bit first. The start bit is indicated by a high-to-low transition of SDA with SCL high; the stop bit is indicated by a low-to-high transition of SDA with SCL high. All other transitions of SDA take place with SCL low.

If the master wishes to write to the slave then it repeatedly sends a byte with the slave sending an ACK bit. (In this situation, the master is in master transmit mode and the slave is in slave receive mode.)

If the master wishes to read from the slave then it repeatedly receives a byte from the slave, the master sending an ACK bit after every byte but the last one. (In this situation, the master is in master receive mode and the slave is in slave transmit mode.)

The master then either ends transmission with a stop bit, or it may send another START bit if it wishes to retain control of the bus for another transfer (a "combined message").

Message protocols

I2C defines basic types of messages, each of which begins with a START and ends with a STOP:

Single message where a master writes data to a slave;

Single message where a master reads data from a slave;

Combined messages, where a master issues at least two reads and/or writes to one or more slaves.

In a combined message, each read or write begins with a START and the slave address. After the first START in a combined message these are also called repeated START bits. Repeated START bits are not preceded by STOP bits, which is how slaves know the next transfer is part of the same message.

Any given slave will only respond to particular messages, as defined by its product documentation.

Pure I2C systems support arbitrary message structures. SMBus is restricted to nine of those structures ...

In practice, most slaves adopt request/response control models, where one or more bytes following a write command are treated as a command or address. Those bytes determine how subsequent written bytes are treated and/or how the slave responds on subsequent reads. Most SMBus operations involve single byte commands.

Messaging example: 24c32 EEPROM

One specific example is the 24c32 type EEPROM, which uses two request bytes that are called Address High and Address Low. (Accordingly, these EEPROMs are not usable by pure SMBus hosts, which only support single byte commands or addresses.)

These bytes are used to address bytes within the 32 kbit (4 kB) supported by that EEPROM; the same two byte addressing is also used by larger EEPROMs, such as 24c512 ones storing 512 kbits (64 kB).

Writing and reading data to these EEPROMs uses a simple protocol: the address is written, and then data is transferred until the end of the message. (That data transfer part of the protocol also makes trouble for SMBus, since the data bytes are not preceded by a count and more than 32 bytes can be transferred at once. I2C EEPROMs smaller than 32 kbits, such as 2 kbit 24c02 ones, are often used on SMBus with inefficient single byte data transfers.)

To write to the EEPROM, a single message is used. After the START, the master sends the chip's bus address with the direction bit clear (write), then sends the two byte address of data within the EEPROM and then sends data bytes to be written starting at that address, followed by a STOP. When writing multiple bytes, all the bytes must be in the same 32 byte page. While it is busy saving those bytes to memory, the EEPROM will not respond to further I2C requests. (That is another incompatibility with SMBus: SMBus devices must always respond to their bus addresses.)

To read starting at a particular address in the EEPROM, a combined message is used. After a START, the master first writes that chip's bus address with the direction bit clear (write) and then the two bytes of EEPROM data address. It then sends a (repeated) START and the EEPROM's bus address with the direction bit set (read). The EEPROM will then respond with the data bytes beginning at the specified EEPROM data address -— a combined message, first a write then a read. The master issues an ACK after each read byte except the last byte, and then a issues a STOP. The EEPROM increments the address after each data byte transferred; multi-byte reads can retrieve the entire contents of the EEPROM using one combined message.

Physical layer

At the physical layer, both SCL and SDA lines are of open-drain design, thus, pull-up resistors are needed. Pulling the line to ground is considered a logical zero while letting the line float is a logical one. This is used as a channel access method. High speed systems (and some others) also add a current source pull up, at least on SCL; this accommodates higher bus capacitance and enables faster rise times.

An important consequence of this is that multiple nodes may be driving the lines simultaneously. If any node is driving the line low, it will be low. Nodes that are trying to transmit a logical one (i.e. letting the line float high) can see this, and thereby know that another node is active at the same time.

When used on SCL, this is called clock stretching and gives slaves a flow control mechanism. When used on SDA, this is called arbitration and ensures there is only one transmitter at a time.

...

Clock stretching using SCL

...

Arbitration using SDA

...

Circuit interconnections

I2C is popular for interfacing peripheral circuits to prototyping systems, such as the Arduino and Raspberry Pi.

I2C does not employ a standardized connector, however, and board designers have created various wiring schemes for I2C interconnections. To minimize damage on 0.1-inch headers, some developers suggested to use alternating signal and power connections of the following wiring schemes should be used: (GND, SCL, VCC, SDA) or (VCC, SDA, GND, SCL).[4]

Buffering and multiplexing

When there are many I2C devices in a system, there can be a need to include bus buffers or multiplexers to split large bus segments into smaller ones. This can be necessary to keep the capacitance of a bus segment below the allowable value or to allow multiple devices with the same address to be separated by a multiplexer.

Many types of multiplexers and buffers exist and all must take into account the fact that I2C lines are specified to be bidirectional. Multiplexers can be implemented with analog switches which can tie one segment to another. Analog switches maintain the bidirectional nature of the lines but do not isolate the capacitance of one segment from another or provide buffering capability.

Buffers can be used to isolate capacitance on one segment from another and/or allow I2C to be sent over longer cables or traces. ...

Timing diagram

Data transfer sequence

Data transfer is initiated with the START bit (S) when SDA is pulled low while SCL stays high. Then, SDA sets the transferred bit while SCL is low (blue) and the data is sampled (received) when SCL rises (green). When the transfer is complete, a STOP bit (P) is sent by releasing the data line to allow it to be pulled up while SCL is constantly high. In order to avoid false marker detection, the level on SDA is changed on the falling edge and is captured on the rising edge of SCL.

Example of bit-banging the I2C Master protocol

...

.END

CooCox I2C read/write EEPROM example program

Coocox I2C master transfer example - 2014feb0301

/**

*****************************************************************************

* @title Master_Transfer.c

* @author CooCox

* @date 11 Oct 2010

* @brief This example describes how to configure I2C working in master mo

* de,

* and Read/Write EEPROM using I2C bus.

*******************************************************************************

*/

////// The above comment is automatically generated by CoIDE ///////////////////

#include "lpc11xx_syscon.h"

#include "lpc11xx_i2c.h"

/*

* I2C Master Mode Transfer Example

*/

void I2CMasterExp()

{

unsigned char send_buf[10] = {0,0, 1,2,3,4,5,6,7};

unsigned char rece_buf[10] = {0};

int i,j;

I2C_M_SETUP_Type transferMCfg;

/* It seems to be bit0 is for I2C, different from

* UM. To be retested along with SSP reset. SSP and I2C

*reset are overlapped, a known bug, for now, both SSP

*and I2C use bit 0 for reset enable. */

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, ENABLE);

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, DISABLE);

I2C_PinsInit(I2CMODE_SF);

I2C_Init(LPC_I2C, 100000);

I2C_Cmd(LPC_I2C, ENABLE);

transferMCfg.sl_addr7bit = 0xA0>>1;

transferMCfg.tx_data = send_buf;

transferMCfg.tx_length = 8;

transferMCfg.rx_data = NULL;

transferMCfg.rx_length = 0;

transferMCfg.retransmissions_max = 3;

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

for(i=0;i<100;i++) {

for(j=0;j<1000;j++);

}

transferMCfg.tx_data = send_buf;

transferMCfg.tx_length = 2;

transferMCfg.rx_data = rece_buf;

transferMCfg.rx_length = 6;

transferMCfg.retransmissions_max = 3;

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

}

.END

/**

*****************************************************************************

* @title Master_Transfer.c

* @author CooCox

* @date 11 Oct 2010

* @brief This example describes how to configure I2C working in master mo

* de,

* and Read/Write EEPROM using I2C bus.

*******************************************************************************

*/

////// The above comment is automatically generated by CoIDE ///////////////////

#include "lpc11xx_syscon.h"

#include "lpc11xx_i2c.h"

/*

* I2C Master Mode Transfer Example

*/

void I2CMasterExp()

{

unsigned char send_buf[10] = {0,0, 1,2,3,4,5,6,7};

unsigned char rece_buf[10] = {0};

int i,j;

I2C_M_SETUP_Type transferMCfg;

/* It seems to be bit0 is for I2C, different from

* UM. To be retested along with SSP reset. SSP and I2C

*reset are overlapped, a known bug, for now, both SSP

*and I2C use bit 0 for reset enable. */

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, ENABLE);

SYSCON_PeriphResetCmd(SYSCON_RSTPeriph_I2C, DISABLE);

I2C_PinsInit(I2CMODE_SF);

I2C_Init(LPC_I2C, 100000);

I2C_Cmd(LPC_I2C, ENABLE);

transferMCfg.sl_addr7bit = 0xA0>>1;

transferMCfg.tx_data = send_buf;

transferMCfg.tx_length = 8;

transferMCfg.rx_data = NULL;

transferMCfg.rx_length = 0;

transferMCfg.retransmissions_max = 3;

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

for(i=0;i<100;i++) {

for(j=0;j<1000;j++);

}

transferMCfg.tx_data = send_buf;

transferMCfg.tx_length = 2;

transferMCfg.rx_data = rece_buf;

transferMCfg.rx_length = 6;

transferMCfg.retransmissions_max = 3;

I2C_MasterTransferData(LPC_I2C, &transferMCfg, I2C_TRANSFER_POLLING);

}

.END

Coocox I2C learning notes

CooCox I2C files - 2014feb0301

/***********************************************************************//**

* @file : lpc11xx_i2c.h

* @brief : Contains all macro definitions and function prototypes

* support for I2C firmware library on LPC11xx

* @version : 1.0

* @date : 22. Jan. 2010

* @author : Coocox

**************************************************************************/

/* Peripheral group ----------------------------------------------------------- */

/** @defgroup I2C

* @ingroup LPC1100CMSIS_FwLib_Drivers

* @{

*/

#ifndef __LPC11XX_I2C_H_

#define __LPC11XX_I2C_H_

/* Includes ------------------------------------------------------------------- */

#include "LPC11xx.h"

#include "lpc11xx_iocon.h"

#include "lpc_types.h"

#ifdef __cplusplus

extern "C"

{

#endif

/* Private Macros ------------------------------------------------------------- */

/** @defgroup I2C_Private_Macros

* @{

*/

/** @defgroup I2C_REGISTER_BIT_DEFINITIONS

* @{

*/

/*******************************************************************//**

* I2C Control Set register description

*********************************************************************/

#define I2C_I2CONSET_AA ((0x04)) /*!< Assert acknowledge flag */

#define I2C_I2CONSET_SI ((0x08)) /*!< I2C interrupt flag */

#define I2C_I2CONSET_STO ((0x10)) /*!< STOP flag */

#define I2C_I2CONSET_STA ((0x20)) /*!< START flag */

#define I2C_I2CONSET_I2EN ((0x40)) /*!< I2C interface enable */

/*******************************************************************//**

* I2C Control Clear register description

*********************************************************************/

/** Assert acknowledge Clear bit */

#define I2C_I2CONCLR_AAC ((1<<2))

/** I2C interrupt Clear bit */

#define I2C_I2CONCLR_SIC ((1<<3))

/** START flag Clear bit */

#define I2C_I2CONCLR_STAC ((1<<5))

/** I2C interface Disable bit */

#define I2C_I2CONCLR_I2ENC ((1<<6))

/********************************************************************//**

* I2C Status Code definition (I2C Status register)

*********************************************************************/

/* Return Code in I2C status register */

#define I2C_STAT_CODE_BITMASK ((0xF8))

/* I2C return status code definitions ----------------------------- */

/** No relevant information */

#define I2C_I2STAT_NO_INF ((0xF8))

/* Master transmit mode -------------------------------------------- */

/** A start condition has been transmitted */

#define I2C_I2STAT_M_TX_START ((0x08))

/** A repeat start condition has been transmitted */

#define I2C_I2STAT_M_TX_RESTART ((0x10))

/** SLA+W has been transmitted, ACK has been received */

#define I2C_I2STAT_M_TX_SLAW_ACK ((0x18))

/** SLA+W has been transmitted, NACK has been received */

#define I2C_I2STAT_M_TX_SLAW_NACK ((0x20))

/** Data has been transmitted, ACK has been received */

#define I2C_I2STAT_M_TX_DAT_ACK ((0x28))

/** Data has been transmitted, NACK has been received */

#define I2C_I2STAT_M_TX_DAT_NACK ((0x30))

/** Arbitration lost in SLA+R/W or Data bytes */

#define I2C_I2STAT_M_TX_ARB_LOST ((0x38))

/* Master receive mode -------------------------------------------- */

/** A start condition has been transmitted */

#define I2C_I2STAT_M_RX_START ((0x08))

/** A repeat start condition has been transmitted */

#define I2C_I2STAT_M_RX_RESTART ((0x10))

/** Arbitration lost */

#define I2C_I2STAT_M_RX_ARB_LOST ((0x38))

/** SLA+R has been transmitted, ACK has been received */

#define I2C_I2STAT_M_RX_SLAR_ACK ((0x40))

/** SLA+R has been transmitted, NACK has been received */

#define I2C_I2STAT_M_RX_SLAR_NACK ((0x48))

/** Data has been received, ACK has been returned */

#define I2C_I2STAT_M_RX_DAT_ACK ((0x50))

/** Data has been received, NACK has been return */

#define I2C_I2STAT_M_RX_DAT_NACK ((0x58))

/* Slave receive mode -------------------------------------------- */

/** Own slave address has been received, ACK has been returned */

#define I2C_I2STAT_S_RX_SLAW_ACK ((0x60))

/** Arbitration lost in SLA+R/W as master */

#define I2C_I2STAT_S_RX_ARB_LOST_M_SLA ((0x68))

/** Own SLA+W has been received, ACK returned */

//#define I2C_I2STAT_S_RX_SLAW_ACK ((0x68))

/** General call address has been received, ACK has been returned */

#define I2C_I2STAT_S_RX_GENCALL_ACK ((0x70))

/** Arbitration lost in SLA+R/W (GENERAL CALL) as master */

#define I2C_I2STAT_S_RX_ARB_LOST_M_GENCALL ((0x78))

/** General call address has been received, ACK has been returned */

//#define I2C_I2STAT_S_RX_GENCALL_ACK ((0x78))

/** Previously addressed with own SLV address;

* Data has been received, ACK has been return */

#define I2C_I2STAT_S_RX_PRE_SLA_DAT_ACK ((0x80))

/** Previously addressed with own SLA;

* Data has been received and NOT ACK has been return */

#define I2C_I2STAT_S_RX_PRE_SLA_DAT_NACK ((0x88))

/** Previously addressed with General Call;

* Data has been received and ACK has been return */

#define I2C_I2STAT_S_RX_PRE_GENCALL_DAT_ACK ((0x90))

/** Previously addressed with General Call;

* Data has been received and NOT ACK has been return */

#define I2C_I2STAT_S_RX_PRE_GENCALL_DAT_NACK ((0x98))

/** A STOP condition or repeated START condition has

* been received while still addressed as SLV/REC

* (Slave Receive) or SLV/TRX (Slave Transmit) */

#define I2C_I2STAT_S_RX_STA_STO_SLVREC_SLVTRX ((0xA0))

/** Slave transmit mode -------------------------------------------- */

/** Own SLA+R has been received, ACK has been returned */

#define I2C_I2STAT_S_TX_SLAR_ACK ((0xA8))

/** Arbitration lost in SLA+R/W as master */

#define I2C_I2STAT_S_TX_ARB_LOST_M_SLA ((0xB0))

/** Own SLA+R has been received, ACK has been returned */

//#define I2C_I2STAT_S_TX_SLAR_ACK ((0xB0))

/** Data has been transmitted, ACK has been received */

#define I2C_I2STAT_S_TX_DAT_ACK ((0xB8))

/** Data has been transmitted, NACK has been received */

#define I2C_I2STAT_S_TX_DAT_NACK ((0xC0))

/** Last data byte in I2DAT has been transmitted (AA = 0);

ACK has been received */

#define I2C_I2STAT_S_TX_LAST_DAT_ACK ((0xC8))

/** Time out in case of using I2C slave mode */

#define I2C_SLAVE_TIME_OUT 0x10000UL

/********************************************************************//**

* I2C Data register definition

*********************************************************************/

/** Mask for I2DAT register*/

#define I2C_I2DAT_BITMASK ((0xFF))

/** Idle data value will be send out in slave mode in case of the actual

* expecting data requested from the master is greater than its sending data

* length that can be supported */

#define I2C_I2DAT_IDLE_CHAR (0xFF)

/********************************************************************//**

* I2C Monitor mode control register description

*********************************************************************/

#define I2C_I2MMCTRL_MM_ENA ((1<<0)) /**< Monitor mode enable */

#define I2C_I2MMCTRL_ENA_SCL ((1<<1)) /**< SCL output enable */

#define I2C_I2MMCTRL_MATCH_ALL ((1<<2)) /**< Select interrupt register match */

#define I2C_I2MMCTRL_BITMASK ((0x07)) /**< Mask for I2MMCTRL register */

/********************************************************************//**

* I2C Data buffer register description

*********************************************************************/

/** I2C Data buffer register bit mask */

#define I2DATA_BUFFER_BITMASK ((0xFF))

/********************************************************************//**

* I2C Slave Address registers definition

*********************************************************************/

/** General Call enable bit */

#define I2C_I2ADR_GC ((1<<0))

/** I2C Slave Address registers bit mask */

#define I2C_I2ADR_BITMASK ((0xFF))

/********************************************************************//**

* I2C Mask Register definition

*********************************************************************/

/** I2C Mask Register mask field */

#define I2C_I2MASK_MASK(n) ((n&0xFE))

/********************************************************************//**

* I2C SCL HIGH duty cycle Register definition

*********************************************************************/

/** I2C SCL HIGH duty cycle Register bit mask */

#define I2C_I2SCLH_BITMASK ((0xFFFF))

/********************************************************************//**

* I2C SCL LOW duty cycle Register definition

*********************************************************************/

/** I2C SCL LOW duty cycle Register bit mask */

#define I2C_I2SCLL_BITMASK ((0xFFFF))

/**

* @}

*/

/**

* @}

*/

/* Public Types --------------------------------------------------------------- */

/** @defgroup I2C_Public_Types

* @{

*/

/** @brief I2C Own slave address setting structure */

typedef struct {

uint8_t SlaveAddrChannel; /**< Slave Address channel in I2C control,

should be in range from 0..3

*/

uint8_t SlaveAddr_7bit; /**< Value of 7-bit slave address */

uint8_t GeneralCallState; /**< Enable/Disable General Call Functionality

when I2C control being in Slave mode, should be:

- ENABLE: Enable General Call function.

- DISABLE: Disable General Call function.

*/

uint8_t SlaveAddrMaskValue; /**< Any bit in this 8-bit value (bit 7:1)

which is set to '1' will cause an automatic compare on

the corresponding bit of the received address when it

is compared to the SlaveAddr_7bit value associated with this

mask register. In other words, bits in SlaveAddr_7bit value

which are masked are not taken into account in determining

an address match

*/

} I2C_OWNSLAVEADDR_CFG_Type;

/** @brief Master transfer setup data structure definitions */

typedef struct

{

uint32_t sl_addr7bit; /**< Slave address in 7bit mode */

uint8_t* tx_data; /**< Pointer to Transmit data - NULL if data transmit

is not used */

uint32_t tx_length; /**< Transmit data length - 0 if data transmit

is not used*/

uint32_t tx_count; /**< Current Transmit data counter */

uint8_t* rx_data; /**< Pointer to Receive data - NULL if data receive

is not used */

uint32_t rx_length; /**< Receive data length - 0 if data receive is

not used */

uint32_t rx_count; /**< Current Receive data counter */

uint32_t retransmissions_max; /**< Max Re-Transmission value */

uint32_t retransmissions_count; /**< Current Re-Transmission counter */

uint32_t status; /**< Current status of I2C activity */

void (*callback)(void); /**< Pointer to Call back function when transmission complete

used in interrupt transfer mode */

} I2C_M_SETUP_Type;

/** @brief Slave transfer setup data structure definitions */

typedef struct

{

uint8_t* tx_data;

uint32_t tx_length;

uint32_t tx_count;

uint8_t* rx_data;

uint32_t rx_length;

uint32_t rx_count;

uint32_t status;

void (*callback)(void);

} I2C_S_SETUP_Type;

/**

* @brief Transfer option type definitions

*/

typedef enum {

I2C_TRANSFER_POLLING = 0, /**< Transfer in polling mode */

I2C_TRANSFER_INTERRUPT /**< Transfer in interrupt mode */

} I2C_TRANSFER_OPT_Type;

/**

* @}

*/

/* Public Macros -------------------------------------------------------------- */

/** @defgroup I2C_Public_Macros

* @{

*/

#define PARAM_I2C_SLAVEADDR_CH(n) ((n<=3))

/** Macro to determine if it is valid SSP port number */

#define PARAM_I2Cx(n) (((uint32_t *)n)==((uint32_t *)LPC_I2C))

/* I2C status values */

#define I2C_SETUP_STATUS_ARBF (1<<8) /**< Arbitration false */

#define I2C_SETUP_STATUS_NOACKF (1<<9) /**< No ACK returned */

#define I2C_SETUP_STATUS_DONE (1<<10) /**< Status DONE */

/*********************************************************************//**

* I2C monitor control configuration defines

**********************************************************************/

#define I2C_MONITOR_CFG_SCL_OUTPUT I2C_I2MMCTRL_ENA_SCL /**< SCL output enable */

#define I2C_MONITOR_CFG_MATCHALL I2C_I2MMCTRL_MATCH_ALL /**< Select interrupt register match */

#define PARAM_I2C_MONITOR_CFG(n) ((n==I2C_MONITOR_CFG_SCL_OUTPUT) || (I2C_MONITOR_CFG_MATCHALL))

/**

* @}

*/

/* Public Functions ----------------------------------------------------------- */

/** @defgroup I2C_Public_Functions

* @{

*/

void I2C_SetClock (I2C_TypeDef *I2Cx, uint32_t target_clock);

void I2C_DeInit(I2C_TypeDef* I2Cx);

void I2C_PinsInit(I2CMODE_Typedef mod);

void I2C_Init(I2C_TypeDef *I2Cx, uint32_t clockrate);

void I2C_Cmd(I2C_TypeDef* I2Cx, FunctionalState NewState);

Status I2C_MasterTransferData(I2C_TypeDef *I2Cx, \

I2C_M_SETUP_Type *TransferCfg, I2C_TRANSFER_OPT_Type Opt);

Status I2C_SlaveTransferData(I2C_TypeDef *I2Cx, \

I2C_S_SETUP_Type *TransferCfg, I2C_TRANSFER_OPT_Type Opt);

void I2C_SetOwnSlaveAddr(I2C_TypeDef *I2Cx, I2C_OWNSLAVEADDR_CFG_Type *OwnSlaveAddrConfigStruct);

uint8_t I2C_GetLastStatusCode(I2C_TypeDef* I2Cx);

void I2C_MonitorModeConfig(I2C_TypeDef *I2Cx, uint32_t MonitorCfgType, FunctionalState NewState);

void I2C_MonitorModeCmd(I2C_TypeDef *I2Cx, FunctionalState NewState);

uint8_t I2C_MonitorGetDatabuffer(I2C_TypeDef *I2Cx);

void I2C_StdIntHandler(void);

/**

* @}

*/

#ifdef __cplusplus

}

#endif

#endif /* __LPC11XX_I2C_H_ */

/**

* @}

*/

/* --------------------------------- End Of File ------------------------------ */

/***********************************************************************//**

* @file : lpc11xx_i2c.c

* @brief : Contains all functions support for I2C firmware library on LPC11xx

* @version : 1.0

* @date : 21. Jan. 2010

* @author : Coocox

**********************************************************************/

/* Peripheral group ----------------------------------------------------------- */

/** @addtogroup I2C

* @{

*/

/* Includes ------------------------------------------------------------------- */

#include "lpc11xx_i2c.h"

#include "lpc11xx_syscon.h"

#include "lpc11xx_libcfg.h"

#if _I2C

/* Private Types -------------------------------------------------------------- */

/** @defgroup I2C_Private_Types

* @{

*/

/**

* @brief I2C device configuration structure type

*/

typedef struct

{

uint32_t txrx_setup; /* Transmission setup */

int32_t dir; /* Current direction phase, 0 - write, 1 - read */

void (*inthandler)(I2C_TypeDef *I2Cx); /* Transmission interrupt handler */

} I2C_CFG_T;

/**

* @}

*/

/* Private Variables ---------------------------------------------------------- */

/** @defgroup I2C_Private_Variables

* @{

*/

/* I2C driver data for I2C0, I2C1 and I2C2 */

static I2C_CFG_T i2cdat[1];

/**

* @}

*/

/* Private Functions ---------------------------------------------------------- */

/** @defgroup I2C_Private_Functions

* @{

*/

/* Generate a start condition on I2C bus (in master mode only) */

static uint32_t I2C_Start (I2C_TypeDef *I2Cx);

/* Generate a stop condition on I2C bus (in master mode only) */

static void I2C_Stop (I2C_TypeDef *I2Cx);

/* I2C send byte subroutine */

static uint32_t I2C_SendByte (I2C_TypeDef *I2Cx, uint8_t databyte);

/* I2C get byte subroutine */

static uint32_t I2C_GetByte (I2C_TypeDef *I2Cx, uint8_t *retdat, Bool ack);

/* I2C interrupt master handler */

void I2C_MasterHandler (I2C_TypeDef *I2Cx);

/* I2C interrupt master handler */

void I2C_SlaveHandler (I2C_TypeDef *I2Cx);

/* Enable interrupt for I2C device */

void I2C_IntCmd (I2C_TypeDef *I2Cx, Bool NewState);

/*--------------------------------------------------------------------------------*/

/**

* @brief Convert from I2C peripheral to number

*/

static int32_t I2C_getNum(I2C_TypeDef *I2Cx){

if (I2Cx == LPC_I2C) {

return (0);

}

return (-1);

}

/***********************************************************************

* Function: I2C_Start

* Purpose: Generate a start condition on I2C bus (in master mode only)

* Parameters:

* i2cdev: Pointer to I2C register

* blocking: blocking or none blocking mode

* Returns: value of I2C status register after generate a start condition

**********************************************************************/

static uint32_t I2C_Start (I2C_TypeDef *I2Cx)

{

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

I2Cx->CONSET = I2C_I2CONSET_STA;

// Wait for complete

while (!(I2Cx->CONSET & I2C_I2CONSET_SI));

I2Cx->CONCLR = I2C_I2CONCLR_STAC;

return (I2Cx->STAT & I2C_STAT_CODE_BITMASK);

}

/***********************************************************************

* Function: I2C_Stop

* Purpose: Generate a stop condition on I2C bus (in master mode only)

* Parameters:

* I2Cx: Pointer to I2C register

* Returns: None

**********************************************************************/

static void I2C_Stop (I2C_TypeDef *I2Cx)

{

/* Make sure start bit is not active */

if (I2Cx->CONSET & I2C_I2CONSET_STA)

{

I2Cx->CONCLR = I2C_I2CONCLR_STAC;

}

I2Cx->CONSET = I2C_I2CONSET_STO;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

}

/***********************************************************************

* Function: I2C_SendByte

* Purpose: Send a byte

* Parameters:

* I2Cx: Pointer to I2C register

* Returns: value of I2C status register after sending

**********************************************************************/

static uint32_t I2C_SendByte (I2C_TypeDef *I2Cx, uint8_t databyte)

{

/* Make sure start bit is not active */

if (I2Cx->CONSET & I2C_I2CONSET_STA)

{

I2Cx->CONCLR = I2C_I2CONCLR_STAC;

}

I2Cx->DAT = databyte & I2C_I2DAT_BITMASK;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

while (!(I2Cx->CONSET & I2C_I2CONSET_SI));

return (I2Cx->STAT & I2C_STAT_CODE_BITMASK);

}

/***********************************************************************

* Function: I2C_GetByte

* Purpose: Get a byte

* Parameters:

* I2Cx: Pointer to I2C register

* Returns: value of I2C status register after receiving

**********************************************************************/

static uint32_t I2C_GetByte (I2C_TypeDef *I2Cx, uint8_t *retdat, Bool ack)

{

if (ack == TRUE)

{

I2Cx->CONSET = I2C_I2CONSET_AA;

}

else

{

I2Cx->CONCLR = I2C_I2CONCLR_AAC;

}

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

while (!(I2Cx->CONSET & I2C_I2CONSET_SI));

*retdat = (uint8_t) (I2Cx->DAT & I2C_I2DAT_BITMASK);

return (I2Cx->STAT & I2C_STAT_CODE_BITMASK);

}

/*********************************************************************//**

* @brief Enable/Disable interrupt for I2C peripheral

* @param[in] I2Cx I2C peripheral selected, should be I2C0, I2C1 or I2C2

* @param[in] NewState New State of I2C peripheral interrupt in NVIC core

* should be:

* - ENABLE: enable interrupt for this I2C peripheral

* - DISABLE: disable interrupt for this I2C peripheral

* @return None

**********************************************************************/

void I2C_IntCmd (I2C_TypeDef *I2Cx, Bool NewState)

{

if (NewState)

{

NVIC_EnableIRQ(I2C_IRQn);

}

else

{

NVIC_DisableIRQ(I2C_IRQn);

}

return;

}

/*********************************************************************//**

* @brief General Master Interrupt handler for I2C peripheral

* @param[in] I2Cx I2C peripheral selected, should be I2C0, I2C1 or I2C2

* @return None

**********************************************************************/

void I2C_MasterHandler (I2C_TypeDef *I2Cx)

{

int32_t tmp;

uint8_t returnCode;

I2C_M_SETUP_Type *txrx_setup;

tmp = I2C_getNum(I2Cx);

txrx_setup = (I2C_M_SETUP_Type *) i2cdat[tmp].txrx_setup;

returnCode = (I2Cx->STAT & I2C_STAT_CODE_BITMASK);

// Save current status

txrx_setup->status = returnCode;

// there's no relevant information

if (returnCode == I2C_I2STAT_NO_INF){

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

return;

}

/* ----------------------------- TRANSMIT PHASE --------------------------*/

if (i2cdat[tmp].dir == 0){

switch (returnCode)

{

/* A start/repeat start condition has been transmitted -------------------*/

case I2C_I2STAT_M_TX_START:

case I2C_I2STAT_M_TX_RESTART:

I2Cx->CONCLR = I2C_I2CONCLR_STAC;

/*

* If there's any transmit data, then start to

* send SLA+W right now, otherwise check whether if there's

* any receive data for next state.

*/

if ((txrx_setup->tx_data != NULL) && (txrx_setup->tx_length != 0)){

I2Cx->DAT = (txrx_setup->sl_addr7bit << 1);

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

} else {

goto next_stage;

}

break;

/* SLA+W has been transmitted, ACK has been received ----------------------*/

case I2C_I2STAT_M_TX_SLAW_ACK:

/* Data has been transmitted, ACK has been received */

case I2C_I2STAT_M_TX_DAT_ACK:

/* Send more data */

if ((txrx_setup->tx_count < txrx_setup->tx_length) \

&& (txrx_setup->tx_data != NULL)){

I2Cx->DAT = *(uint8_t *)(txrx_setup->tx_data + txrx_setup->tx_count);

txrx_setup->tx_count++;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

}

// no more data, switch to next stage

else {

next_stage:

// change direction

i2cdat[tmp].dir = 1;

// Check if any data to receive

if ((txrx_setup->rx_length != 0) && (txrx_setup->rx_data != NULL)){

// check whether if we need to issue an repeat start

if ((txrx_setup->tx_length != 0) && (txrx_setup->tx_data != NULL)){

// Send out an repeat start command

I2Cx->CONSET = I2C_I2CONSET_STA;

I2Cx->CONCLR = I2C_I2CONCLR_AAC | I2C_I2CONCLR_SIC;

}

// Don't need issue an repeat start, just goto send SLA+R

else {

goto send_slar;

}

}

// no more data send, the go to end stage now

else {

// success, goto end stage

txrx_setup->status |= I2C_SETUP_STATUS_DONE;

goto end_stage;

}

}

break;

/* SLA+W has been transmitted, NACK has been received ----------------------*/

case I2C_I2STAT_M_TX_SLAW_NACK:

/* Data has been transmitted, NACK has been received -----------------------*/

case I2C_I2STAT_M_TX_DAT_NACK:

// update status

txrx_setup->status |= I2C_SETUP_STATUS_NOACKF;

goto retry;

//break;

/* Arbitration lost in SLA+R/W or Data bytes -------------------------------*/

case I2C_I2STAT_M_TX_ARB_LOST:

// update status

txrx_setup->status |= I2C_SETUP_STATUS_ARBF;

default:

goto retry;

//break;

}

}

/* ----------------------------- RECEIVE PHASE --------------------------*/

else if (i2cdat[tmp].dir == 1){

switch (returnCode){

/* A start/repeat start condition has been transmitted ---------------------*/

case I2C_I2STAT_M_RX_START:

case I2C_I2STAT_M_RX_RESTART:

I2Cx->CONCLR = I2C_I2CONCLR_STAC;

/*

* If there's any receive data, then start to

* send SLA+R right now, otherwise check whether if there's

* any receive data for end of state.

*/

if ((txrx_setup->rx_data != NULL) && (txrx_setup->rx_length != 0)){

send_slar:

I2Cx->DAT = (txrx_setup->sl_addr7bit << 1) | 0x01;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

} else {

// Success, goto end stage

txrx_setup->status |= I2C_SETUP_STATUS_DONE;

goto end_stage;

}

break;

/* SLA+R has been transmitted, ACK has been received -----------------*/

case I2C_I2STAT_M_RX_SLAR_ACK:

if (txrx_setup->rx_count < (txrx_setup->rx_length - 1)) {

/*Data will be received, ACK will be return*/

I2Cx->CONSET = I2C_I2CONSET_AA;

}

else {

/*Last data will be received, NACK will be return*/

I2Cx->CONCLR = I2C_I2CONSET_AA;

}

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

break;

/* Data has been received, ACK has been returned ----------------------*/

case I2C_I2STAT_M_RX_DAT_ACK:

// Note save data and increase counter first, then check later

/* Save data */

if ((txrx_setup->rx_data != NULL) && (txrx_setup->rx_count < txrx_setup->rx_length)){

*(uint8_t *)(txrx_setup->rx_data + txrx_setup->rx_count) = (I2Cx->DAT & I2C_I2DAT_BITMASK);

txrx_setup->rx_count++;

}

if (txrx_setup->rx_count < (txrx_setup->rx_length - 1)) {

/*Data will be received, ACK will be return*/

I2Cx->CONSET = I2C_I2CONSET_AA;

}

else {

/*Last data will be received, NACK will be return*/

I2Cx->CONCLR = I2C_I2CONSET_AA;

}

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

break;

/* Data has been received, NACK has been return -------------------------*/

case I2C_I2STAT_M_RX_DAT_NACK:

/* Save the last data */

if ((txrx_setup->rx_data != NULL) && (txrx_setup->rx_count < txrx_setup->rx_length)){

*(uint8_t *)(txrx_setup->rx_data + txrx_setup->rx_count) = (I2Cx->DAT & I2C_I2DAT_BITMASK);

txrx_setup->rx_count++;

}

// success, go to end stage

txrx_setup->status |= I2C_SETUP_STATUS_DONE;

goto end_stage;

//break;

/* SLA+R has been transmitted, NACK has been received ------------------*/

case I2C_I2STAT_M_RX_SLAR_NACK:

// update status

txrx_setup->status |= I2C_SETUP_STATUS_NOACKF;

goto retry;

//break;

/* Arbitration lost ----------------------------------------------------*/

case I2C_I2STAT_M_RX_ARB_LOST:

// update status

txrx_setup->status |= I2C_SETUP_STATUS_ARBF;

default:

retry:

// check if retransmission is available

if (txrx_setup->retransmissions_count < txrx_setup->retransmissions_max){

// Clear tx count

txrx_setup->tx_count = 0;

I2Cx->CONSET = I2C_I2CONSET_STA;

I2Cx->CONCLR = I2C_I2CONCLR_AAC | I2C_I2CONCLR_SIC;

txrx_setup->retransmissions_count++;

}

// End of stage

else {

end_stage:

// Disable interrupt

I2C_IntCmd(I2Cx, FALSE);

// Send stop

I2C_Stop(I2Cx);

// Call callback if installed

if (txrx_setup->callback != NULL){

txrx_setup->callback();

}

}

break;

}

}

}

/*********************************************************************//**

* @brief General Slave Interrupt handler for I2C peripheral

* @param[in] I2Cx I2C peripheral selected, should be LPC_I2C

* @return None

**********************************************************************/

void I2C_SlaveHandler (I2C_TypeDef *I2Cx)

{

int32_t tmp;

uint8_t returnCode;

I2C_S_SETUP_Type *txrx_setup;

uint32_t timeout;

tmp = I2C_getNum(I2Cx);

txrx_setup = (I2C_S_SETUP_Type *) i2cdat[tmp].txrx_setup;

returnCode = (I2Cx->STAT & I2C_STAT_CODE_BITMASK);

// Save current status

txrx_setup->status = returnCode;

// there's no relevant information

if (returnCode == I2C_I2STAT_NO_INF){

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

return;

}

switch (returnCode)

{

/* No status information */

case I2C_I2STAT_NO_INF:

I2Cx->CONSET = I2C_I2CONSET_AA;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

break;

/* Reading phase -------------------------------------------------------- */

/* Own SLA+R has been received, ACK has been returned */

case I2C_I2STAT_S_RX_SLAW_ACK:

/* General call address has been received, ACK has been returned */

case I2C_I2STAT_S_RX_GENCALL_ACK:

I2Cx->CONSET = I2C_I2CONSET_AA;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

break;

/* Previously addressed with own SLA;

* DATA byte has been received;

* ACK has been returned */

case I2C_I2STAT_S_RX_PRE_SLA_DAT_ACK:

/* DATA has been received, ACK hasn been return */

case I2C_I2STAT_S_RX_PRE_GENCALL_DAT_ACK:

/*

* All data bytes that over-flow the specified receive

* data length, just ignore them.

*/

if ((txrx_setup->rx_count < txrx_setup->rx_length) \

&& (txrx_setup->rx_data != NULL)){

*(uint8_t *)(txrx_setup->rx_data + txrx_setup->rx_count) = (uint8_t)I2Cx->DAT;

txrx_setup->rx_count++;

}

I2Cx->CONSET = I2C_I2CONSET_AA;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

break;

/* Previously addressed with own SLA;

* DATA byte has been received;

* NOT ACK has been returned */

case I2C_I2STAT_S_RX_PRE_SLA_DAT_NACK:

/* DATA has been received, NOT ACK has been returned */

case I2C_I2STAT_S_RX_PRE_GENCALL_DAT_NACK:

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

break;

/*

* Note that: Return code only let us know a stop condition mixed

* with a repeat start condition in the same code value.

* So we should provide a time-out. In case this is really a stop

* condition, this will return back after time out condition. Otherwise,

* next session that is slave receive data will be completed.

*/

/* A Stop or a repeat start condition */

case I2C_I2STAT_S_RX_STA_STO_SLVREC_SLVTRX:

// Temporally lock the interrupt for timeout condition

I2C_IntCmd(I2Cx, FALSE);

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

// enable time out

timeout = I2C_SLAVE_TIME_OUT;

while(1){

if (I2Cx->CONSET & I2C_I2CONSET_SI){

// re-Enable interrupt

I2C_IntCmd(I2Cx, TRUE);

break;

} else {

timeout--;

if (timeout == 0){

// timeout occur, it's really a stop condition

txrx_setup->status |= I2C_SETUP_STATUS_DONE;

goto s_int_end;

}

}

}

break;

/* Writing phase -------------------------------------------------------- */

/* Own SLA+R has been received, ACK has been returned */

case I2C_I2STAT_S_TX_SLAR_ACK:

/* Data has been transmitted, ACK has been received */

case I2C_I2STAT_S_TX_DAT_ACK:

/*

* All data bytes that over-flow the specified receive

* data length, just ignore them.

*/

if ((txrx_setup->tx_count < txrx_setup->tx_length) \

&& (txrx_setup->tx_data != NULL)){

I2Cx->DAT = *(uint8_t *) (txrx_setup->tx_data + txrx_setup->tx_count);

txrx_setup->tx_count++;

}

I2Cx->CONSET = I2C_I2CONSET_AA;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

break;

/* Data has been transmitted, NACK has been received,

* that means there's no more data to send, exit now */

/*

* Note: Don't wait for stop event since in slave transmit mode,

* since there no proof lets us know when a stop signal has been received

* on slave side.

*/

case I2C_I2STAT_S_TX_DAT_NACK:

I2Cx->CONSET = I2C_I2CONSET_AA;

I2Cx->CONCLR = I2C_I2CONCLR_SIC;

txrx_setup->status |= I2C_SETUP_STATUS_DONE;

goto s_int_end;

//break;

// Other status must be captured

default:

s_int_end:

// Disable interrupt

I2C_IntCmd(I2Cx, FALSE);

I2Cx->CONCLR = I2C_I2CONCLR_AAC | I2C_I2CONCLR_SIC | I2C_I2CONCLR_STAC;

// Call callback if installed